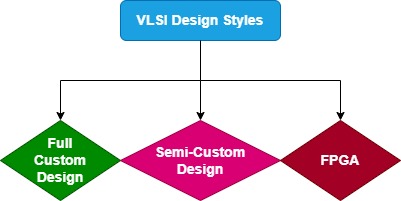

VLSI Design Styles

PLEASE CLICK ON THIS LINK TO SEMI-CUSTOM DESIGN ASIC Full Custom Design: Full custom design in VLSI (Very Large Scale Integration) refers to the process of designing and implementing a custom integrated circuit (IC) using a bottom-up approach. In this approach, the designer starts from scratch and creates the circuit layout and wiring patterns manually, instead of using pre-designed building blocks or standard cells. In full custom design, the designer has complete control over the layout, placement, and interconnects of all the components in the circuit. This approach allows for the highest level of optimization and customization, as the designer can create a circuit that is specifically tailored to meet the exact requirements of the application. However, full custom design is a time-consuming and complex process that requires a high level of expertise and skill. It typically involves multiple iterations of design, simulation, and verification to ensure that the final prod...