RTL Design Practice Guide I - Sequential Logic - D Latch

2.1 Latch

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - US

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN2.1.1 D Latch

A

D latch is a type of digital circuit that is used to store a single bit of

information. It has only one input, which is called the ‘din’ input. When the

latch is enabled, the output of the latch is set to the value of the data input.

When the latch is disabled, the output of the latch remains in its previous

state.

A

D latch can be constructed using logic gates such as NAND gates or NOR gates.

In RTL (Register Transfer Level) design practice, the D latch can be designed

using Verilog or VHDL, and simulate to test its functionality.

D

latches are commonly used in digital systems for various purposes, such as

holding data, buffering signals, and synchronizing signals between different

parts of the system. They can also be combined with other digital circuits, such

as flip-flops and counters, to create more complex digital designs. Overall,

understanding the operation and implementation of D latches is an important

part of RTL design practice.

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - US

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN

2.1.2 Block Diagram:

A

D latch has a control input called enable ‘en’, when the enable input is high,

the latch is transparent, meaning that the output ‘qout’ will follow the input ‘din’.

When the enable input is low, the latch is opaque, meaning that the output ‘qout’

will hold its previous state.

Figure

2.1 – Shows the block diagram of a simple latch digital design circuit without

a reset functionality:

Figure

2.1 – D Latch block diagram

Figure

2.1 – Shows the block diagram of a simple latch digital design circuit with a reset

functionality:

Figure

2.2 – D Latch with reset block diagram

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN

2.1.3 RTL Schematic:

The

RTL schematic of a D latch shows the behaviour of the circuit at the

register-transfer level, while describes the flow of data between register and

functional units. In this schematic, the D latch is composed of two NAND gates

or two NOR gates (S and R), with their output cross-coupled to create a

feedback loop. The input D represents the data to be stored, while the output Q

represents the stored value.

The

’G’ input is an enable signal that determines whether the latch is transparent

(G = 1) or opaque (G = 0). When G = 1, the latch is transparent, meaning that

the output Q will follow the input D. When EN = 0, the latch is opaque, meaning

that the output Q will hold its previous state.

Figure

2.3 – shows the RTL schematic of a D latch digital circuit without a reset

functionality:

Figure

2.3 – D latch RTL schematic without Reset

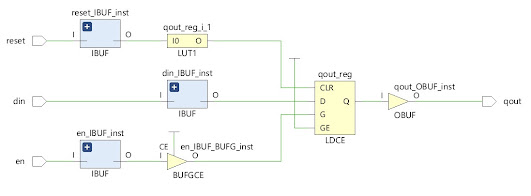

Figure 2.4 -shows the RTL schematic of a D latch

digital circuit with a reset functionality:

Figure

2.4 – D latch RTL schematic with Reset

Overall,

the RTL schematic of a D latch shows how the circuit operates at a higher level

of abstraction, focusing on the flow of data and control signals between registers

and functional units.

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - US

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN

2.1.4 RTL Synthesis:

RTL

synthesis is the process of automatically translating a high-level RTL description

into a gate-level netlist using synthesis tools. The synthesis tools map the

RTL description of a circuit into a set of gates that can be implemented using

standard cell libraries. The goal of RTL synthesis is to optimize the netlist

area, timing, and power, while preserving the functionality of the original RTL

design.

A

D-latch can be implemented in hardware using logic gates, such as NAND or NOR

gates, but when synthesizing the RTL code for a latch digital design circuit,

Vivado uses LUTs to implement the logic function. The LUTs are configurable

memory elements that can store the truth table of a logic function.

Figure

2.5- shows the synthesis implementation of a D latch digital design circuit without

a reset functionality, generate using Vivado synthesis tool:

Figure

2.5 – D latch synthesis implementation without Reset

Figure

2.6- shows the synthesis implementation of a D latch digital design circuit

with a reset functionality, generate using Vivado synthesis tool:

Figure

2.6 – D latch synthesis implementation with Reset

Overall,

the Vivado Synthesis Schematic with LUT for a D-latch provides a visual

representation of how the RTL code for a latch digital design circuit is synthesized

into a netlist of logic gates, specifically LUTs, which are used to implement

the logic function of the D-latch in hardware.

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - US

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN

2.1.5 FPGA Implementation:

FPGA

(Field-Programmable Gate Array) implementation is the process of programming an

FPGA device to create a digital circuit that performs a specific function. FPGA

devices are integrated circuits that can be programmed and reprogrammed to

perform a wide range of digital functions, making them ideal for variety of

applications, including digital signal processing, image and video processing,

and machine learning.

Figure

2.7- shows the implementation flow of a FPGA design

Figure

2.7 – D latch implementation flow diagram

The following is the D latch implementation without

reset functionality:

Reference Device: xcau15p-ffvb676-2-e

LUT -

0

FF - 0

BRAM -

0

URAM - 0

DSP -

0

IO - 3

GT

- 0

BUFG -

1

MMCM -

0

PLL - 0

PCIe -

0

FPGA

Resource for a D latch without Reset

The following is the D latch implementation with reset

functionality:

Reference Device: xcau15p-ffvb676-2-e

LUT -

1

FF - 0

BRAM -

0

URAM - 0

DSP -

0

IO - 4

GT

- 0

BUFG -

1

MMCM -

0

PLL - 0

PCIe -

0

FPGA Resource for a D latch with Reset

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - US

PLEASE CLICK TO GET RTL DESIGN PRACTICE GUIDE - IN

2.1.6 Hardware Description Language:

2.1.6.1

System Verilog: Latch without Reset

The

following System Verilog code illustrate the implementation of a latch digital

design circuit without reset functionality:

module

dlatch_sv (

input logic din,

input logic en,

output logic qout

);

always_comb begin

if (en)

qout = din;

end

endmodule

This

code defines a module called ‘dlatch_sv’ that has three ports: an input ‘din’,

an input ‘en’, and an output ‘qout’. The module implements a D latch, which is

a digital circuit that stores a single bit of data.

The

‘always_comb’ block describes the behaviour of the module. It checks the value

of the ‘en’ input and and, if it is true, sets the output ‘qout’ to the value

of the input ‘din’. If ‘en’ is false, the output ‘qout’ will retain its

previous value.

Note

that this code assumes that ‘din’, ‘en’, and ‘qout’ are all single bits. If you

need to create a multi-bit latch, you’ll need to modify the code accordingly.

2.1.6.2 Verilog: Latch without Reset

The

following Verilog code illustrate the implementation of a simple latch digital

circuit without reset functionality:

module

dlatch (

input din,

input en,

output reg qout

);

always @ (en)

begin

if (en)

qout = din;

end

endmodule

This

code defines a module called ‘dlatch’ that has three ports: an input ‘din’, an

input ‘en’, and an output ‘qout’. The module implements a D latch, which is a

digital circuit that stores a single bit of data.

The

‘always @’ block describes the behaviour of the module. If triggers whenever

either the ‘en’ or ‘din’ input changes. If ‘en’ is true, the output ‘qout’ will

be set to the value of ‘din’. If ‘en’ is false, the output ‘qout’ will retain

its previous value.

2.1.6.3 System Verilog: Latch with Reset

The

following System Verilog code illustrate the implementation of a latch digital

design circuit with reset:

module

dlatch_reset_sv (

input logic din,

input logic en,

input logic reset,

output logic qout

);

always_comb begin

if (reset)

qout = 0;

else if (en)

qout = din;

end

endmodule

This

code defines a module called ‘dlatch_reset_sv’ that has four ports: an input ‘din’,

an input ‘en’, an input ‘reset’, and an output ‘qout’. The module implements a

D latch with a reset functionality, which is a digital circuit that stores a

single bit of data.

The

‘always_comb’ block describes the behaviour of the module. It checks the value of

the ‘reset’ input and, if it is true, sets the output ‘qout’ to 0, effectively resetting

it. If ‘reset’ is false, the block then checks the value of the ‘enable’ input,

and if it is true, sets the output ‘qout’ to the value of the input ‘din’. If

both ‘reset’ and ‘enable’ are false, the output ‘qout’ will retain its previous

value.

2.1.6.4 Verilog: Latch with Reset

The

following Verilog code illustrate the implementation of a simple latch digital

design with reset functionality:

module

dlatch_reset (

input din,

input en,

input reset,

output reg qout

);

always

@ (en or reset or din)

begin

if (!reset)

qout = 1'b0;

else if (en)

qout = din;

end

endmodule

This

code defines a module called ‘dlatch_reset’ that has four ports: an input ‘din’,

an input ‘en’, an input ‘reset’, and an output ‘qout’. The module implements a

D latch with a reset functionality, which is a digital circuit that stores a

single bit of data.

The

‘always @’ block describes the behaviour of the module. It triggers whenever

either the ‘en’, ‘din’, or ‘reset’ input changes. If ‘reset’ is true, the

output ‘qout’ will be set to 0. If the ‘en’ is true, the output ‘qout’ will be

set to the value of ‘din’. If both ‘reset’ and ‘en’ are false, the output ‘qout’

will retain its previous value.

2.1.7 Questions to ask design perspective

How can you prevent race conditions from occurring in

the latch digital circuit?

What are setup and hold time requirements for the

input and outputs of the latch, and how can you ensure they are met?

How can you minimize the power consumption of the

latch digital circuit?

What steps can you take to ensure proper signal integrity

in the latch digital circuit?

What timing constraints must be met in the latch

digital circuit, and how can you ensure they are met?

How can you ensure proper operation of a finite state

machine that uses the latch digital circuit as a building block?

2.1.8 Problem statements for RTL design

practice:

Implement a D latch with asynchronous reset

Implement a D latch with enable input

Implement a D latch with edge-triggered input

Comments

Post a Comment